分频器(DIV_TSPC)设计

- 前言

-

- 一、DIV工作原理

- 二、DIV电路设计

-

- (1)32分频原理图

- (2)D触发器原理图

- (3)D锁存器原理图

- (4)三输入与非门原理图

- 三、DIV仿真测试

-

- 32分频器测试原理图

- DIV分频测试结果

- 参考文献

-

- 各部分链接链接:

前言

本文主要内容是对分频器(DIV_TSPC) 设计模块设计设计进行阐述,基于TSPC动态触发器结构,更好的适应高频应用,内容包括工作原理、电路结构、仿真结果各部分内容。

一、DIV工作原理

在CPPLL电路中,分频器的功能是将VCO的输出频率降到1/N倍数,即分频到较低倍数上。然后PFD会对参考信号以及分频器分频VCO信号后的信号进行相位比较。分频器可分为再生式分频器(Regenerative Frequency Divider,RFD)、真单相时钟分频器(True Single Phase Clock, TSPC)、电流模逻辑分频器(Current Mode Logic, CML)、注入锁定分频器( Injection-Locked Frequency Divider, ILFD)、相位切换分频器等。其中, 真单相时钟分频器(TSPC)是一种典型的单端触发器结构,依赖节点上的寄生电容存储电位信息,其功耗很小。

最常用的分频器是由D触发器(DFF) 构成的,而所有的分频器都是基于二分频。二分频实际上是一个具有两个状态的最简单的时序状态机。二分频器的原理如图4-6-1所示。

32分频器可以看作是二分频电路的扩展。它是通过简单地级联5个除以2的电路来实现的,如图4-6-2所示。该电路的输入为 VCO 产生的频率 fin=fclkf_{in}=f_{clk}fin=fclk 的正弦信号,输出为占空比 1/21/21/2 的矩形信号,其频率fout=fclk/32f_{out}=f_{clk}/32fout=fclk/32,输出至 PFD 将其与参考频率进行比较。

对于速度和功耗要求较高的锁相环PLL而言,一般结构的 DFF 组成的分频器不能满足要求。本次主要采用 TSPC 结构来完成分频器的设计。相比较于传统的锁存器同时需要真实的和互补的时钟信号而言,TSPC电路技术只使用一个时钟信号,从不反转,并适合静态和动态 CMOS 电路。边缘触发的D触发器通常在使用动态逻辑的集成高速操作中实现。这意味着数字输出存储在寄生设备电容上,而设备没有过渡。TSPC动态触发器 以小功率和高速执行触发器操作。然而动态触发器通常不会在静态或低时钟速度下工作:如果有足够的时间,泄漏路径可能会释放足够的寄生电容,从而导致触发器进入无效状态,因此在 高频电路中TSPC有着更加优异的性能。

TSPC动态触发器的工作基于预充电和放电两个过程,由 TSPC 组成的 D 触发器翻转有四个基本阶段分别称为预充电N(PN)、预充电 P(PP)、非预充电 N(SN)和非预充电 P(SP)。本文所采用的 TSPC 动态触发器电路如图4-6-3所示,该架构通过在QN输出端后面增加反相级,从而作为D输出端。

电路共分为四级,当时钟信号 CLK=0 时,M2 和 M6 开启,第一级作为一个开启的锁存器接收输入信号,而第二级的输出节点Y被预充电。在此期间,由于 M8 仍然保持关断状态,因此第三级和第四级保持维持上一时刻的状态。紧接着当时钟产生上升沿时,即CLK=1,此时 M2 和 M6 关断,M4 和 M8 开启,第一级关断且第二级开始维持上一时刻的状态。同时,第三级对节点 Y 进行采样,并将采样值传送到QN输出。第四级通过反相器将 QN 进行反相得到 Q 逻辑输出端。

假设工作频率为foutf_{out}fout,则对应的时间常数可以表示为:

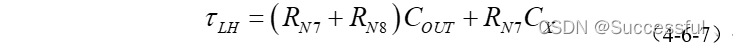

时间常数分别由上升时间常数 τLHτ_{LH}τLH 和下降时间常数τHLτ_{HL}τHL组成:

时间常数和输出节点的等效电容和等效电阻有关,可以表示为:

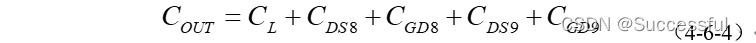

在 TSPC 结构的 D 触发器电路结构中,第三级电路由 M7-M9 组成,如图4-6-4所示,输出电容可以表示为:

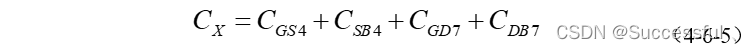

其中,CLC_LCL 为第四级反相器的输入电容,CXC_XCX 为 M7 漏端的寄生电容,可以表示为:

对于上升时间常数而言,其主要由 M9 决定:

对于下降时间常数而言,其主要由 M7-M8 决定:

RN7 和 RN8 表示为NMOS管 M7 和 M8 的等效电阻,并由下式表示:

分频器电路的主要设计指标如下所示:

(1)分频器的分频数N

根据频率综合器性能指标的不同,设计出合理的分频比 N ,从而采用不同的电路结构来实现。分频比N的取值影响电路结构的复杂度, N 越大,电路结构就越复杂。

(2)最高工作频率

指在分频器任意分频比均正常工作时,输入信号所能实现的最高工作频率。影响分频器最高工作频率的因素有很多,主要包括 MOS 管尺寸、电路的基本结构、输入时钟信号、逻辑形式等,但从根源上来说可以概括为电路结构和电路的寄生参数。为了提高分频器工作速度,可以通过改进工艺来实现;但在给定工艺时,可以优化电路结构,减小电路中的寄生参数以及主要反馈通路的延时来提高电路的最高工作频率。

(3)功耗

使用不同的电路结构,所需的功耗自然也不同,在实际电路设计中,根据电路的指标要求,合理选择分频器的电路结构在一定程度上降低整个电路的功耗。

(4)输出相位噪声

指输出信号的抖动情况,改善输出相噪的方法是提高脉冲边沿的陡度和输入信号脉冲对输出信号脉冲进行选通。

(5)稳定性和可靠性

以上所列的性能指标反映了 PLL 对于分频器的主要要求,不同的指标之间是相互矛盾的。在实际的电路设计过程中,根据电路设计的要求合理优化各项指标。通常来说,矛盾的主要方面为分频器的工作速度即工作频率。

二、DIV电路设计

本文采用分频系数为 32 的整数分频器,它由五个基于 D触发器 的 2 分频器构成,其中D触发器采用 TSPC D 触发器。其原理图和测试原理图分别由下图4-6-5、4-6-6给出,具体模块的电路实现由图4-6-7、4-6-8、4-6-9给出。

(1)32分频原理图

(2)D触发器原理图

(3)D锁存器原理图

(4)三输入与非门原理图

三、DIV仿真测试

32分频器测试原理图

将五个二分频器级联后进行仿真得到如图 4-6-10所示的波形,可见输出信号的频率是输入信号频率的 1/32,实现了 32分频 的功能。

DIV分频测试结果

参考文献

[1]周龙龙. CMOS锁相环关键技术研究与设计[D].电子科技大学,2021.

[2]金豪强. 应用于连续波雷达频率源的0.1~3GHz低功耗4/5双模分频器设[D].东南大学,2020.

[3]唐欣. 面向于3GPP LTE和IEEE802.11系统的频率综合器的研究[D].东南大学,2018.

[4]黄胜. 高性能CMOS频率综合器关键技术研究[D].西安电子科技大学,2019.

[5]朱晓锐. 应用于射频超宽带锁相环的高速低功耗分频器研究与设计[D].广东工业大学,2018.

| 分割线 |

各部分链接链接:

频率综合器(Frequency Synthesizer,FS)设计 链接:【模拟集成电路】频率综合器(Frequency Synthesizer,FS)设计

鉴频鉴相器(PFD)设计 链接:【模拟集成电路】鉴频鉴相器设计(Phase Frequency Detector,PFD)

电荷泵(CP)设计 链接:【模拟集成电路】电荷泵(CP)设计

压控振荡器(VCO)设计 链接:【模拟集成电路】宽摆幅压控振荡器(VCO)设计

环路滤波器(LPF)设计 链接:【模拟集成电路】环路滤波器(LPF)设计

支付宝扫一扫

支付宝扫一扫 微信扫一扫

微信扫一扫

.png)

.png)