文章目录

- 触发器

-

- 一、概述

- 二、SR锁存器(Set-Reset Latch)

- 三、触发器

-

- 1.电平触发的触发器(同步RS触发器)

- 2.边沿触发的触发器(边沿RS触发器)

- 3.脉冲触发的触发器(主从RS触发器)

- 四、触发器按逻辑功能的分类

-

- 1.SR触发器

- 2.JK触发器

- 3.T触发器

- 4.D触发器

触发器

一、概述

定义:

能够存储一位二值信号的基本单元电路统称为触发器

触发器的两个基本特点:

(1)具有两个能自行保持的稳定状态,用来表示逻辑状态的0和1,或二进制数的0和1;

(2)根据不同的输入信号可以置成0或1状态

二、SR锁存器(Set-Reset Latch)

SR锁存器是静态存储单元中最基本,也是电路结构最简单的一种,也称为基本RS触发器。通常其由两个或非门或与非门组成。

1.SR锁存器的约束条件为:S * R = 0

2.将S称为置位端;R称为复位端

3.将此电路称为直接置位、复位锁存器(Set-Reset Latch)

三、触发器

一、触发器与锁存器的不同在于:触发器除了置1,置0输入端以外,又增加了一个触发信号输入端。

二、只有当触发信号到来时,触发器才能按照输入的置1,置0信号置成相应的状态,并保持下去。

三、将此触发信号称为时钟信号(CLOCK),记为CLK。

四、当系统中有多个触发器需要同时动作时,就可以用同一个时钟信号作为同步控制信号。

五、触发信号的工作方式可分为:(1)电平触发;(2)边沿触发;(3)脉冲触发

1.电平触发的触发器(同步RS触发器)

1.当CLK=0时,门G3,G4的输出始终停在1状态,S、R端的信号无法通过这两个门而影响输出状态,输出保持原来的状态不变。

2.当触发信号CLK变成高电平时,S、R信号才能通过门G3、G4,“触发”电路发生变化,使Q和Q’根据S、R信号改变状态。

3.因此,将CLK的这种控制方式称为电平触发方式。

1.只有当CLK变为有效电平,触发器才能接收输入信号,并按照输入信号将触发器的输出置成相应的状态。

2.在CLK=1的全部时间里,S和R状态的变化都可能引起输出状态的改变。在CLK回到0以后,触发器保存的是CLK回到0以前瞬间的状态。

3.综上所述,若在CLK=1期间,S、R的状态多次发生变化,则触发器输出的状态也将发生多次翻转,这就降低了触发器的抗干扰能力。

2.边沿触发的触发器(边沿RS触发器)

为了提高触发器的可靠性,提高抗干扰能力,希望触发器的次态仅仅取决于CLK信号下降沿或上升沿到达时刻输入信号的状态,而在此之前和之后输入状态的变化对触发器的次态没有影响。因此,产生了边沿触发的触发器。

边沿触发方式的动作特点为:触发器的次态仅取决于时钟信号的上升沿或下降沿到达时,输入的逻辑状态。而在这以前或以后,输入信号的变化对触发器输出的状态没有影响。这一点有效地提高了触发器的抗干扰能力,提高了电路的可靠性。

3.脉冲触发的触发器(主从RS触发器)

也称FF1为主触发器,FF2为从触发器。

1.触发器的翻转分两步动作:第一步,当CLK以高电平为有效信号时,在CLK=1期间主动触发器输入端(S、R)的信号,被置成相应的状态,而从触发器不动;第二步,CLK下降沿到来时从触发器按照主触发器的状态翻转,所以输出Q和Q’端状态的改变发生在CLK的下降沿。(若CLK以低电平为有效信号,则Q和Q’状态的变化发生在CLK的上升沿。)

2.因为主触发器本质上为一个电平触发SR触发器,所以在CLK=1的全部时间里输入信号都将对主触发器起控制作用。

由于存在以上两个动作特点,在CLK=1期间输入信号发生过变化以后,CLK下降沿到达时,从触发器的状态不一定能按照此刻输入信号的状态来确定,而必须考虑整个CLK=1期间里输入信号的变化过程才能确定触发器的次态。

因此,在使用脉冲触发的触发器时必须注意:****只有在CLK=1的全部时间里,输入状态始终未变的条件下,用CLK下降沿到达时输入的状态决定触发器的次态才一定是对的。否则,必须考虑CLK=1期间输入状态的全部变化过程,才能确定CLK下降沿到达时触发器的次态。

四、触发器按逻辑功能的分类

1.SR触发器

凡在时钟信号作用下,逻辑功能符合表中特性所规定的逻辑功能者,无论触发方式如何,均称为SR触发器。

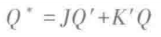

2.JK触发器

凡在时钟信号作用下,逻辑功能符合表中特性所规定的逻辑功能者,无论触发方式如何,均称为JK触发器。

3.T触发器

当控制信号T=1时,每来一个时钟信号它的状态就翻转一次;而当T=0时,时钟信号到达后它的状态保持不变。具备这种逻辑功能的触发器称为T触发器。

4.D触发器

凡在时钟信号作用下,逻辑功能符合表中特性所规定的逻辑功能者,无论触发方式如何,均称为D触发器。

支付宝扫一扫

支付宝扫一扫 微信扫一扫

微信扫一扫

.png)

.png)

.png)